## EE 330 Lecture 33

- High Gain Amplifiers

- Current Sources and Mirrors

### Fall 2023 Exam Schedule

Exam 1 Friday Sept 22

Exam 2 Friday Oct 20

Exam 3 Friday Nov. 17

Final Monday Dec 11 12:00 – 2:00 p.m.

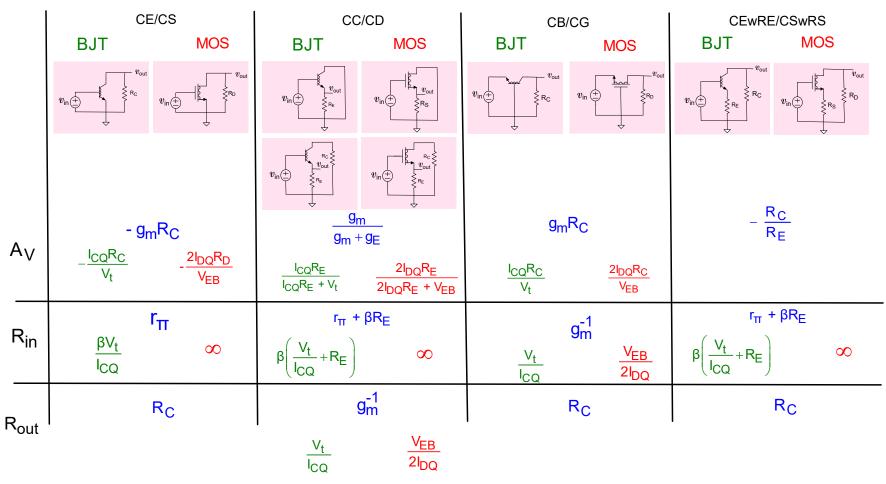

#### Basic Amplifier Application Gain Table

(not two-port models for the four structures)

Can use these equations only when small signal circuit is EXACTLY like that shown!!

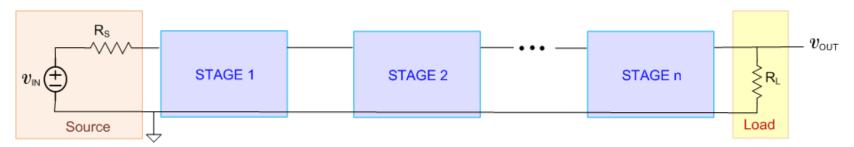

### Cascaded Amplifier Analysis and Operation

#### Adjacent Stage Coupling Only

Systematic Methods of Analysis/Design will be Developed

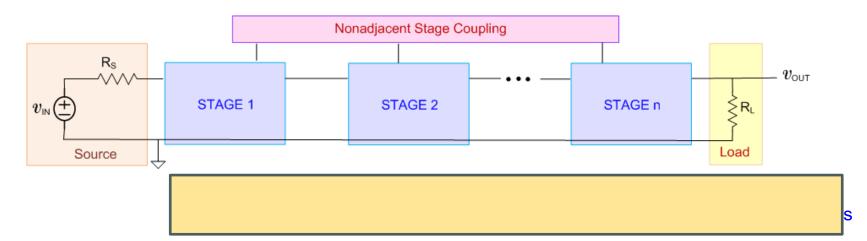

#### One or more couplings of nonadjacent stages

Review From Previous Lecture

### Cascaded Amplifier Analysis and Operation

Case 2: One or more stages are not unilateral

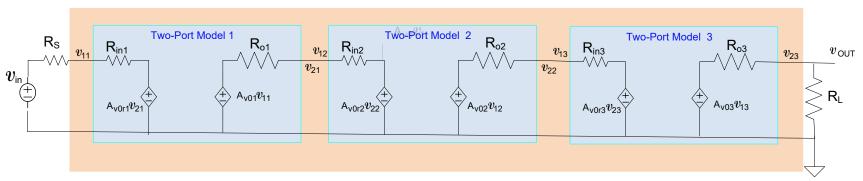

#### Standard two-port cascade

Analysis by creating new two-port of entire amplifier quite tedious because of the reverse-gain elements

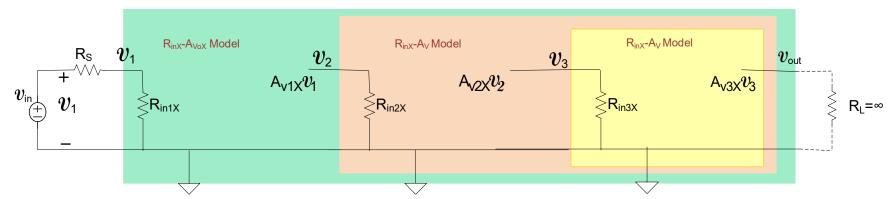

#### ➤ Right-to-left nested R<sub>inx</sub>,A<sub>VKX</sub> approach

- R<sub>inx</sub> includes effects of <u>all</u> loading

- A<sub>VKX</sub> is the voltage ratio from input to output of a stage

- A<sub>VKX</sub>'s include all loading

- Can not change any loading without recalculating everthing!

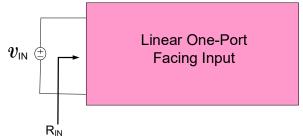

## Review From Previous Lecture Review: Small-signal equivalent of a one-port

## Review From Previous Lecture Review: Small-signal equivalent of a one-port

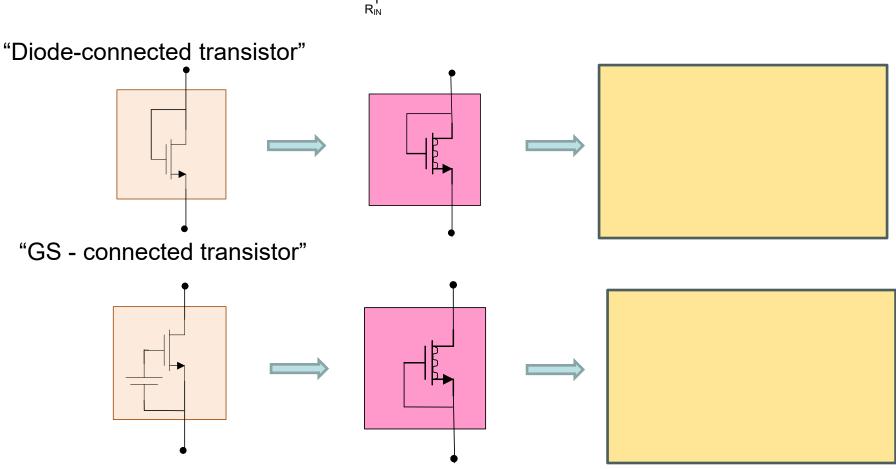

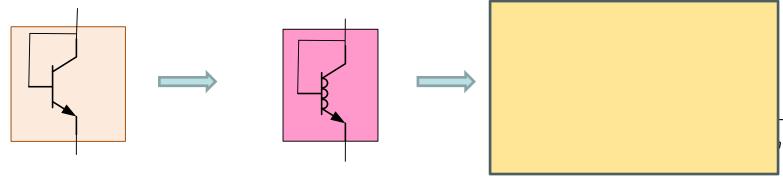

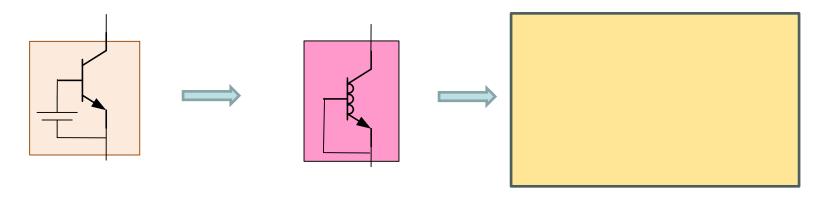

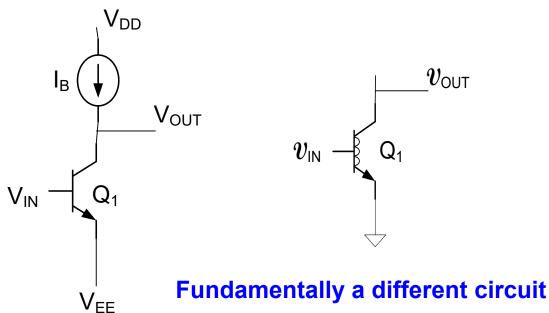

"Diode-connected transistor"

"BE - connected transistor"

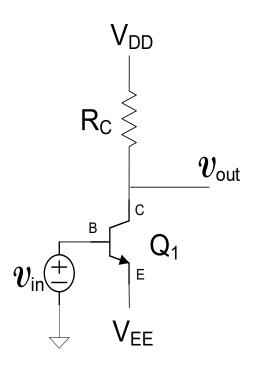

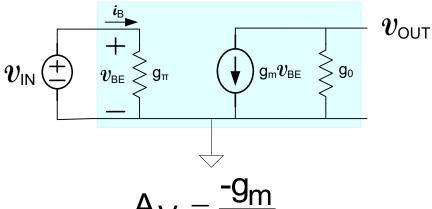

$$A_V = \frac{-g_m}{g_0 + G_C} \cong -g_m R_C$$

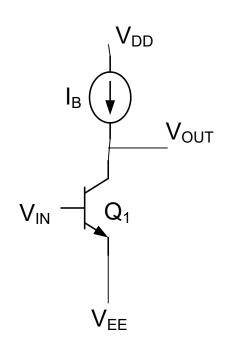

To make the gain large, it appears that all one needs to do is make R<sub>C</sub> large!

$$A_V \cong -g_m R_C = \frac{-I_{CQ} R_C}{V_t}$$

But  $V_t$  is fixed at approx 25mV and to keep Q1 in forward active with large signal swing,  $I_{CQ}R_C < (V_{DD} - V_{EE})/2$

$$|A_V| < \frac{V_{DD} - V_{EE}}{2V_t}$$

If  $V_{DD} - V_{EE} = 5V$ ,

$$|A_V| < \frac{5V}{2 \cdot 25mV} = 100$$

- Gain is practically limited with this supply voltage to around 100

- And in extreme case, limited to about 200 with this supply voltage with very small signal swing

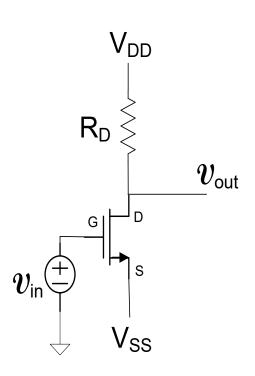

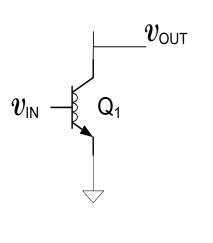

$$A_V = \frac{-g_m}{g_0 + G_D} \cong -g_m R_D$$

To make the gain large, it appears that all one needs to do is make  $R_D$  large !

$$A_{V} \cong -g_{m}R_{D} = \frac{-2I_{DQ}R_{D}}{V_{EB}}$$

But  $V_{EB}$  is practically limited to around 100mV and for good signal swing,  $I_{DO}R_D < (V_{DD}V_{SS})/2$

$$\left|A_{V}\right| < \frac{V_{DD} - V_{SS}}{V_{FB}}$$

If  $V_{DD}$  - $V_{SS}$ =5V and  $V_{EB}$ =100mV,

$$|A_V| < \frac{5V}{100mV} = 50$$

Gain is practically limited with this supply voltage to around 50

Are these fundamental limits on the gain of the BJT and MOS Amplifiers?

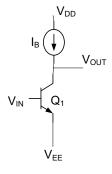

$$A_V = \frac{-g_m}{0} = -\infty$$

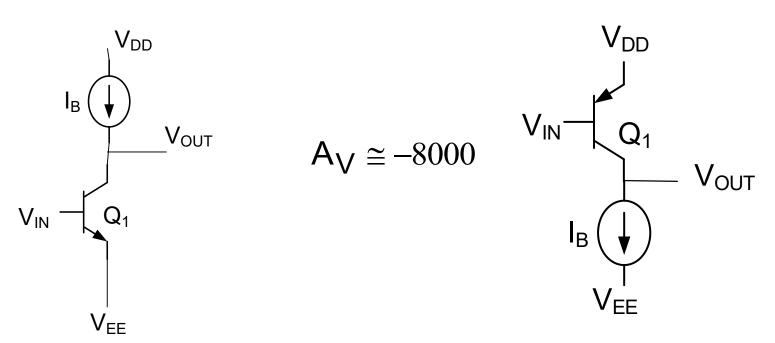

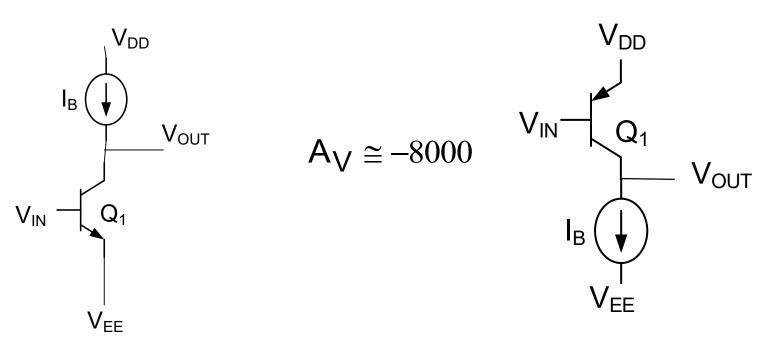

Current source is biasing Q<sub>1</sub>

This gain is very large!

Too good to be true!

Need better model of BJT and MOS device (but we already have it)!

$$A_{V} = \frac{-9m}{g_{0}}$$

$$A_{V} = \frac{-I_{CQ}}{V_{t}I_{CQ}/V_{AF}} = -\frac{V_{AF}}{V_{t}}$$

$$A_V = -\frac{V_{AF}}{V_t} \cong \frac{200V}{25mV} = -8000$$

This gain is very large (but realistic)!

And no design parameters affect the gain

But how can we make a current source?

Same gain with both npn and pnp transistors

How can we build the ideal current source?

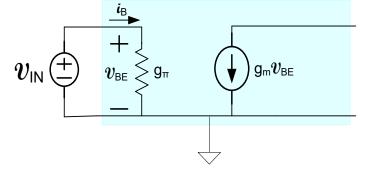

What is the small-signal model of an actual current source?

Same gain with both npn and pnp transistors

Will now focus on creating current sources and then return to using these current sources to build high gain amplifiers.

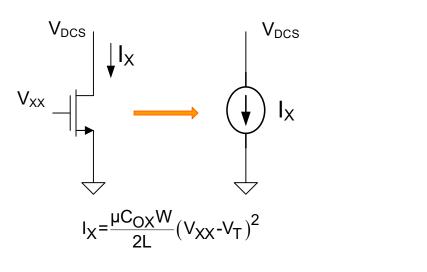

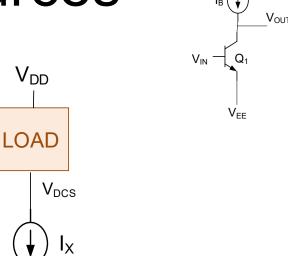

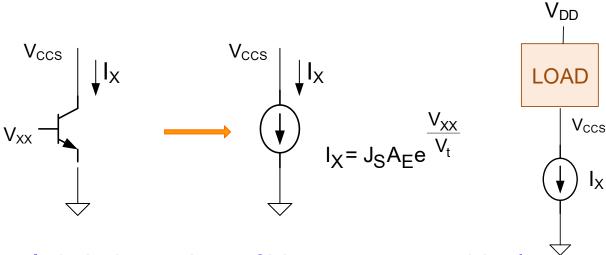

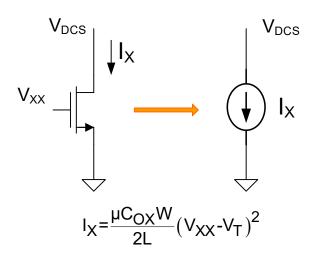

a "sinking" current source

Since  $I_X$  is independent of  $V_{DCS}$ , acts as an ideal current source (with this model)

Termed a "sinking" current source since current is pulled out of the load

If  $V_{XX}$  is available, each dc current source requires only one additional transistor!

Have several methods for generating  $V_{XX}$  from  $V_{DD}$  (see HW problems)

But how good is this current "sink"?

And may not have both MOS and Bipolar devices in most processes! But for the npn high-gain amplifier considered need a sourcing current

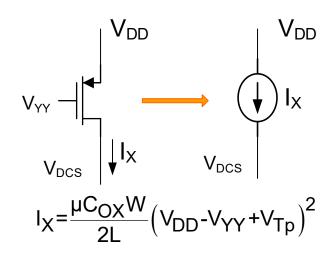

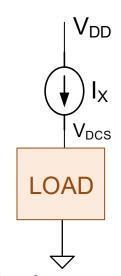

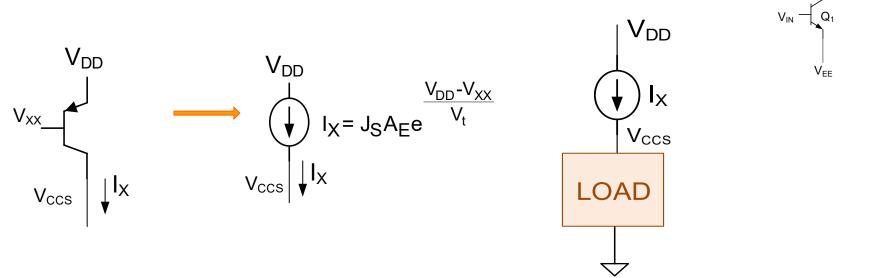

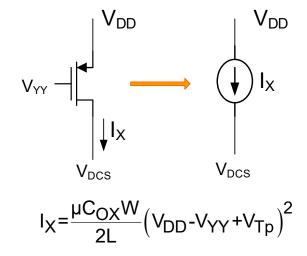

a "sourcing" current source

Since  $I_X$  is independent of  $V_{DCS}$ , acts as an ideal current source (with this model)

Termed a "sourcing" current source since pushed into the load

If  $V_{YY}$  is available, each dc current source requires only one additional transistor!

Have several methods for generating  $V_{YY}$  from  $V_{DD}$  (see HW problems)

But how good is this current "source"?

And may not have both MOS and Bipolar devices in most processes!

a "sinking" current source

Since I<sub>X</sub> is independent of V<sub>CCS</sub>, acts as an ideal current source (with this model)

Termed a "sinking" current source since current is pulled out of the load

If  $V_{XX}$  is available, each dc current source requires only one additional transistor!

Have several methods for generating  $V_{XX}$  from  $V_{DD}$  (see HW problems)

But for the npn high-gain amplifier considered need a sourcing current

But how good is this current "sink"?

a "sourcing" current source

Since  $I_X$  is independent of  $V_{CCS}$ , acts as an ideal current source (with this model)

Termed a "sourcing" current source since pushed into the load

If  $V_{XX}$  is available, each dc current source requires only one additional transistor !

Current highly sensitive to  $V_{xx}$  if generated with dc voltage source

Have several methods for generating  $V_{XX}$  from  $V_{DD}$  (see HW problems)

But how good is this current "source"?

Before addressing the issue of how a current source is designed, will consider another circuit that uses current source biasing

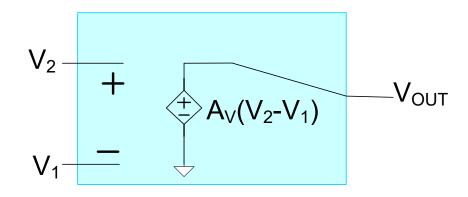

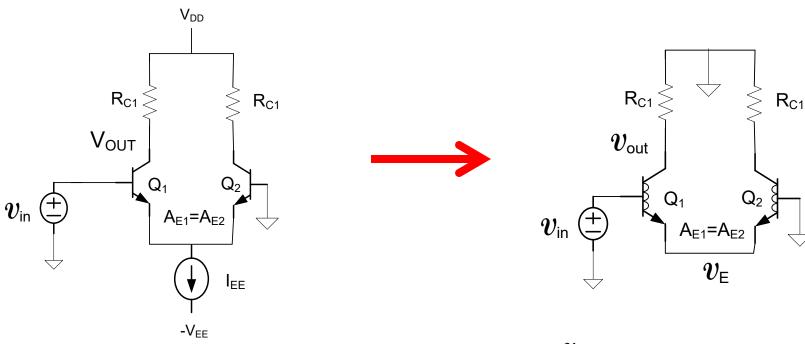

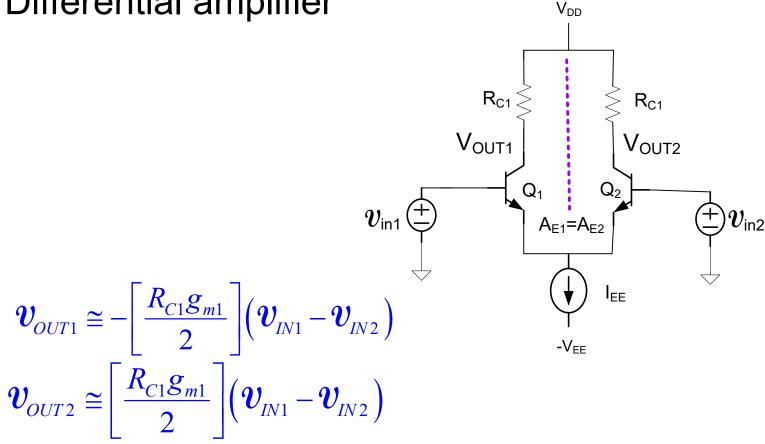

### The Basic Differential Amplifier

If A<sub>V</sub> is large

Operational Amplifier (Op Amp)

# Example: Determine the voltage gain of the following circuit

Since symmetric when  $v_{\scriptscriptstyle {

m IN}}$ =0

$$I_{C1Q} = I_{C2Q} = \frac{I_{EE}}{2}$$

$$g_{m1} = g_{m2} = \frac{I_{EE}}{2V_{\bullet}}$$

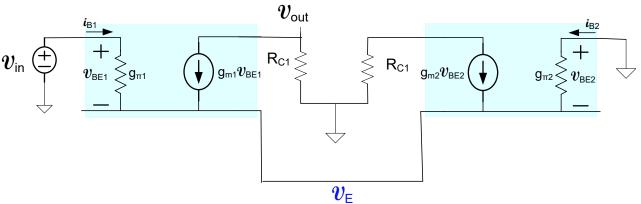

#### Determine the voltage gain of the Example: following circuit

$$v_{E}(g_{\pi 1} + g_{\pi 1}) = g_{\pi 1}v_{IN} + g_{m1}(v_{IN} - v_{E}) + g_{m2}(-v_{E})$$

$$v_{E}(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2}) = v_{IN}(g_{m1} + g_{\pi 1})$$

$$v_{E}(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2}) = v_{IN}(g_{m1} + g_{\pi 1})$$

$$v_{E}(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2}) = v_{IN}(g_{m1} + g_{\pi 1})$$

$$v_{E}(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2}) = v_{IN}(g_{m1} + g_{\pi 1})$$

$$V_E(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2}) = V_{IN}(g_{m1} + g_{\pi 1})$$

$$\mathbf{v}_{E} = \frac{(g_{m1} + g_{\pi 1})}{(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2})} \mathbf{v}_{IN}$$

$$\mathbf{v}_{OUT} = -R_{C1}\mathbf{g}_{m1}\mathbf{v}_{IN} \left[ 1 - \frac{\left( \mathbf{g}_{m1} + \mathbf{g}_{\pi1} \right)}{\left( \mathbf{g}_{\pi1} + \mathbf{g}_{\pi2} + \mathbf{g}_{m1} + \mathbf{g}_{m2} \right)} \right]$$

$$\mathbf{v}_{OUT} = -R_{C1}g_{m1}\mathbf{v}_{IN} \left[ \frac{g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2} - (g_{m1} + g_{\pi 1})}{(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2})} \right]$$

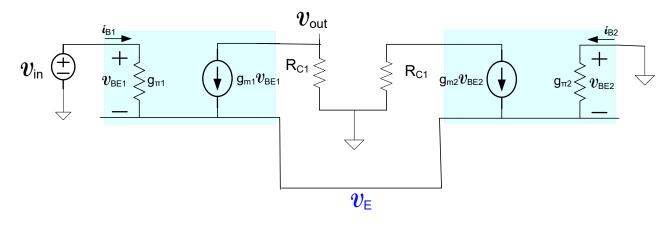

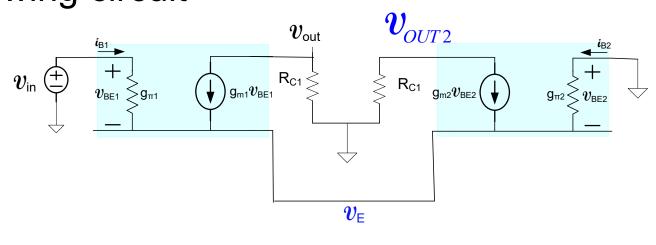

# Example: Determine the voltage gain of the following circuit

$$v_{OUT} = -R_{C1}g_{m1}v_{IN} \left[ \frac{g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2} - (g_{m1} + g_{\pi 1})}{(g_{\pi 1} + g_{\pi 2} + g_{m1} + g_{m2})} \right]$$

$$v_{OUT} \cong -R_{C1}g_{m1}v_{IN} \left[ \frac{g_{m2}}{(g_{m1} + g_{m2})} \right]$$

$$v_{OUT} \cong \left[ \frac{-R_{C1}g_{m1}}{2} \right] v_{IN}$$

$$v_{OUT} \cong \left[ \frac{R_{C1}g_{m1}}{2} \right] v_{IN}$$

### Differential amplifier

- Very useful circuit

- This is a basic Op Amp

- Uses a current source and V<sub>DD</sub> for biasing (no biasing resistors or caps!)

- But needs a dc current source !!!!

But how good are these current sources?

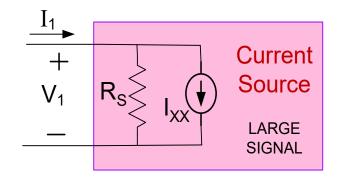

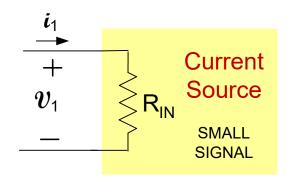

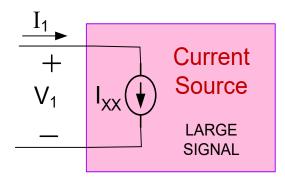

## Model of dc Current Source

"Reasonable dc Current Source"

$I_{XX}$  independent of  $V_1$  and t,  $R_S$  large

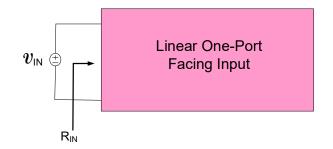

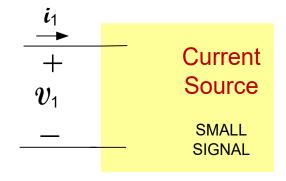

Small-signal model of dc current source (since one-port)

want R<sub>IN</sub> large

#### Ideal dc Current Source

I<sub>XX</sub> independent of V<sub>1</sub> and t

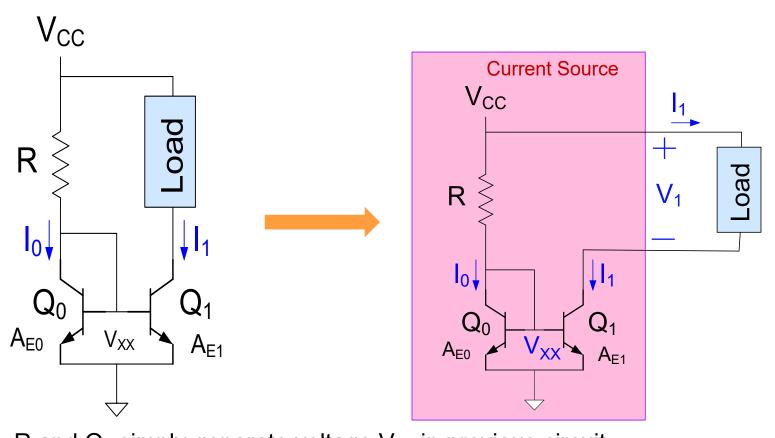

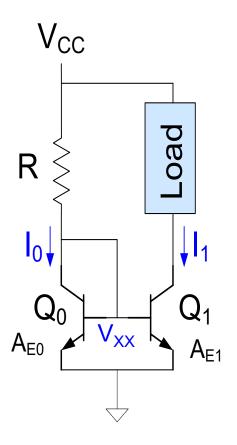

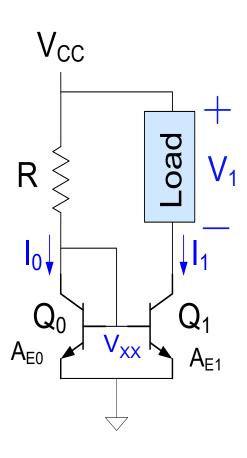

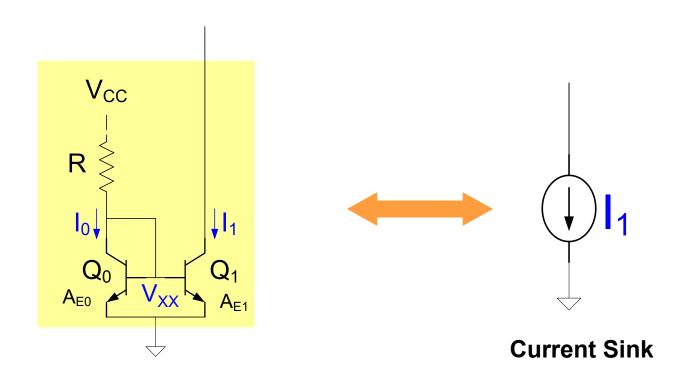

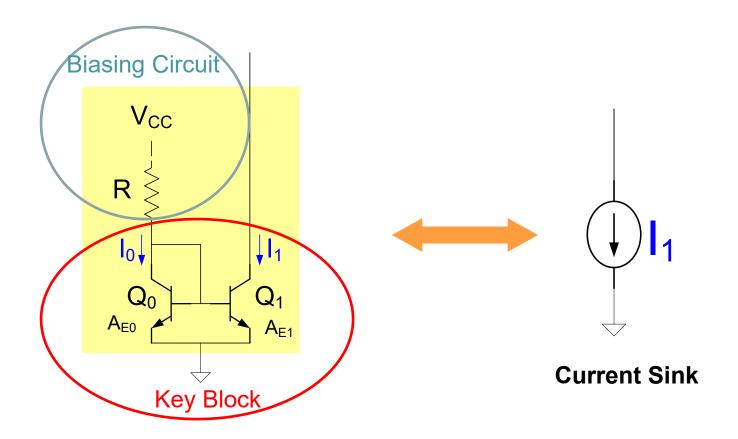

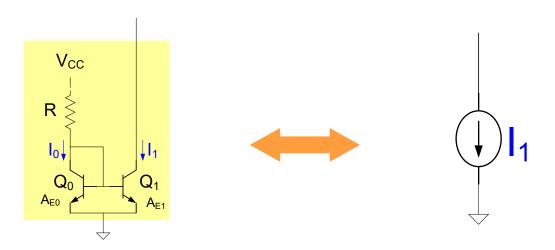

Will show circuit in red behaves as a current source

R and  $Q_0$  simply generate voltage  $V_{XX}$  in previous circuit But sensitivity of  $I_1$  is much smaller than using voltage source for generating  $V_{XX}$

$$I_0 \cong \frac{\left(V_{CC}\text{-}0.6V\right)}{R}$$

If the base currents are neglected

$$I_0 \cong \frac{\left(V_{CC}\text{-}0.6V\right)}{R}$$

If the base currents are neglected

$$I_0 = J_S A_{E0} e^{\frac{V_{BE0}}{V_t}}$$

$I_1 = J_S A_{E1} e^{\frac{V_{BE1}}{V_t}}$

since V<sub>BE1</sub>=V<sub>BE2</sub>

$$I_1 \cong \left(\frac{A_{E1}}{A_{E0}}\right) I_0 = \left(\frac{A_{E1}}{A_{E0}}\right) \frac{V_{CC} - 0.6V}{R}$$

Note I<sub>1</sub> is not a function of V<sub>1</sub>

Behaves as a current sink! So is ideal with this model!!

And does not require an additional dc voltage source !!!

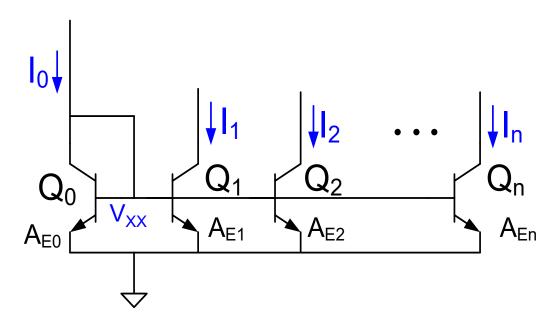

- Multiple Outputs Possible

- Can be built for sourcing or sinking currents

- Also useful as a current amplifier

- MOS counterparts work very well and are not plagued by base current

Two ways to look at this circuit:

- Q<sub>0</sub> and R bias Q<sub>1</sub>

- R biases the Q<sub>0</sub> : Q<sub>1</sub> block

Current Sources are Seldom Available in Basic Laboratories:

Biasing of board-level and discrete electronic circuits is usually done with voltage sources, resistors, and capacitors

Biasing resistors and capacitors are used very sparingly in MOS circuits

Will show on-chip current sources can be very small

Biasing of on-chip circuits is often done with current sources instead of R's and C's

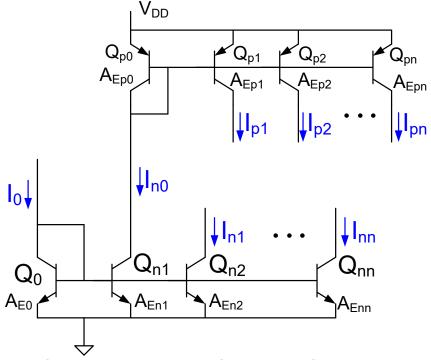

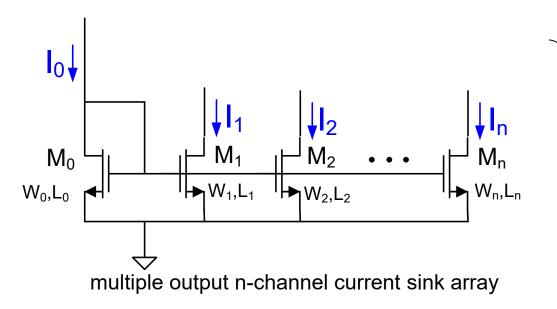

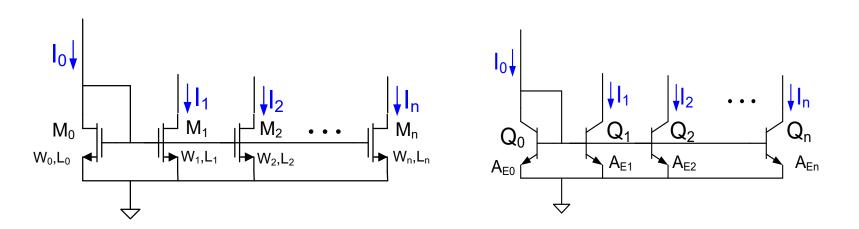

Multiple-Output Bipolar Current Sink

If the base currents are neglected

$$\mathbf{I}_{k} = \begin{bmatrix} \mathbf{A}_{Ek} \\ \mathbf{A}_{E0} \end{bmatrix} \mathbf{I}_{0}$$

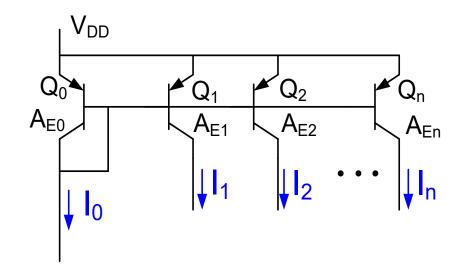

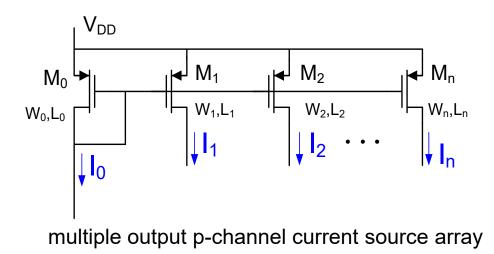

Multiple-Output Bipolar Current Source

If the base currents are neglected

$$\mathbf{I}_{k} = \begin{vmatrix} \mathbf{A}_{Ek} \\ \mathbf{A}_{E0} \end{vmatrix} \mathbf{I}_{0}$$

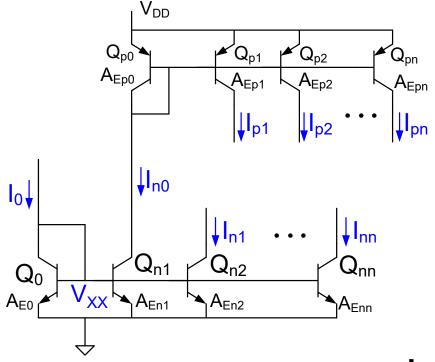

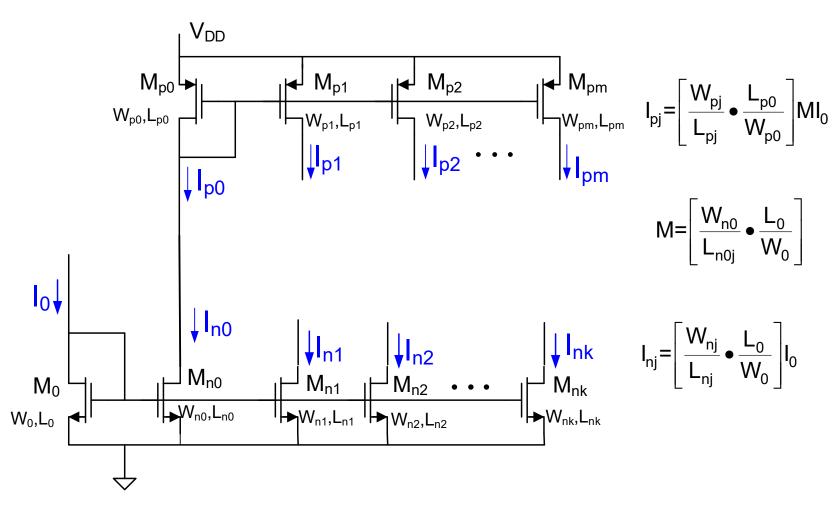

**Multiple-Output Bipolar Current Source and Sink**

$$I_{nk} = ? I_{pk} = ?$$

Multiple-Output Bipolar Current Source and Sink If the base currents are neglected

$$I_{nk} = \left[\frac{A_{Enk}}{A_{E0}}\right]I_0 \qquad I_{pk} = \left[\frac{A_{En1}}{A_{E0}}\right]\left|\frac{A_{Epk}}{A_{Ep0}}\right|I_0$$

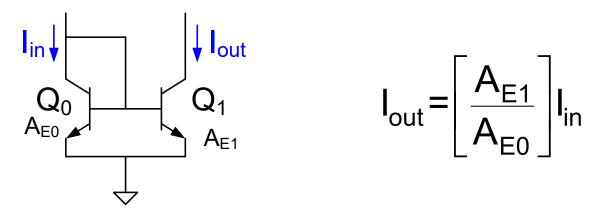

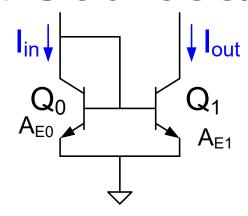

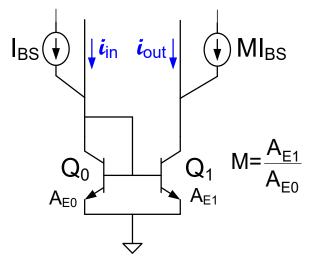

This circuit is termed a "current mirror"

Will re-derive the transfer characteristics of the current mirror assuming  $I_{\rm B}$  is small compared to  $I_{\rm C}$

$$\begin{vmatrix} I_{\text{IN}} = J_{\text{S}} A_{\text{E0}} e^{\frac{V_{\text{BE}}}{V_{\text{t}}}} \\ I_{\text{OUT}} = J_{\text{S}} A_{\text{E1}} e^{\frac{V_{\text{BE}}}{V_{\text{t}}}} = \frac{J_{\text{S}} A_{\text{E1}} e^{\frac{V_{\text{BE}}}{V_{\text{t}}}}}{J_{\text{S}} A_{\text{E0}} e^{\frac{V_{\text{BE}}}{V_{\text{t}}}}} = \frac{A_{\text{E1}}}{A_{\text{E0}}}$$

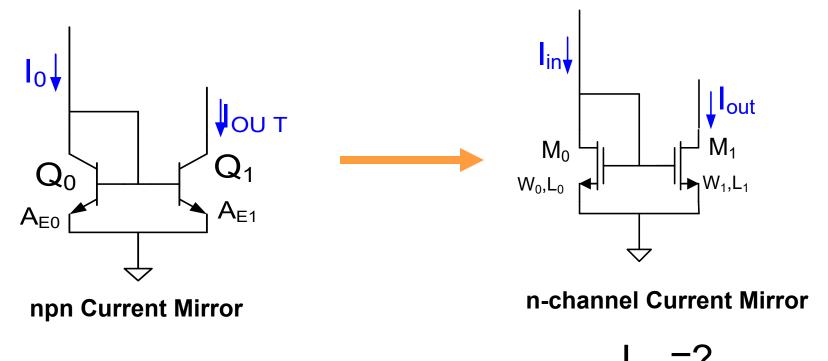

#### npn Current Mirror

If the base currents are neglected

$$I_{\text{out}} = \left[ \frac{A_{\text{E1}}}{A_{\text{E0}}} \right] I_{\text{in}}$$

- Output current linearly dependent on lin

- Small-signal and large-signal relationships the same since linear

- Serves as a current amplifier

- Widely used circuit

But I<sub>in</sub> must be positive!

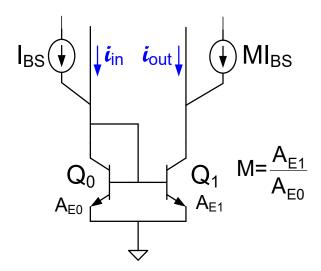

npn current mirror amplifier

$$\frac{i_{\text{OUT}} + \text{MI}_{\text{BS}}}{i_{\text{in}} + \text{I}_{\text{BS}}} = \text{M}$$

$$i_{\text{OUT}} + \text{MI}_{\text{BS}} = \text{M} \left( i_{\text{in}} + \text{I}_{\text{BS}} \right)$$

$$i_{\text{OUT}} + \text{MI}_{\text{BS}} = \text{M} \left( i_{\text{in}} + \text{I}_{\text{BS}} \right)$$

$$\frac{i_{\text{OUT}}}{i_{\text{in}}} = \text{M}$$

$$i_{\text{in}}$$

But  $I_{\text{BS}} + i_{\text{in}} > 0$ !

npn current mirror amplifier

$$i_{\text{out}} = \left[\frac{A_{\text{E1}}}{A_{\text{E0}}}\right] i_{\text{in}}$$

Amplifies both positive and negative currents (provided i<sub>IN</sub>>-I<sub>BS</sub>)

**Current amplifiers are easy to build!!**

Current gain can be accurately controlled with appropriate layout !!

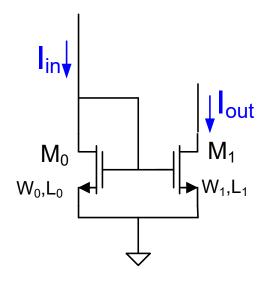

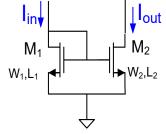

#### n-channel Current Mirror

$$I_{in} = \frac{\mu C_{OX} W_0}{2L_0} (V_{GS0} - V_{T0})^2$$

$$I_{out} = \frac{\mu C_{OX} W_1}{2L_1} (V_{GS1} - V_{T1})^2$$

If process parameters are matched, it follows that

$$\mathbf{I}_{\text{out}} = \left[ \frac{\mathbf{W}_1}{\mathbf{W}_0} \frac{\mathbf{L}_0}{\mathbf{L}_1} \right] \mathbf{I}_{\text{in}}$$

- Current mirror gain <u>can</u> be accurately controlled!

- Layout is important to get accurate gain (for both MOS and BJT)

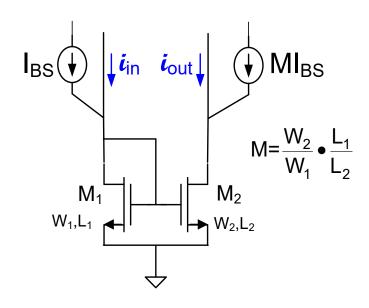

### n-channel current mirror current amplifier

$$i_{\text{out}} = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right] i_{\text{in}}$$

Amplifies both positive and negative currents

$$\mathbf{I}_{k} = \left[ \frac{\mathbf{W}_{k}}{\mathbf{W}_{0}} \frac{\mathbf{L}_{0}}{\mathbf{L}_{k}} \right] \mathbf{I}_{0}$$

multiple sourcing and sinking current outputs

m and k may be different Often M=1

## Current Sources/Mirrors Summary

npn Current Mirror

$$I_{\text{out}} = \left[ \frac{A_{\text{E1}}}{A_{\text{E0}}} \right] I_{\text{in}}$$

n-channel Current Mirror

$$\mathbf{I}_{\text{out}} = \left[ \frac{\mathbf{W}_1}{\mathbf{W}_0} \frac{\mathbf{L}_0}{\mathbf{L}_1} \right] \mathbf{I}_{\text{in}}$$

- Current mirror gain <u>can</u> be accurately controlled!

- Layout is important to get accurate gain (for both MOS and BJT)

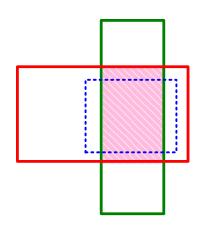

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

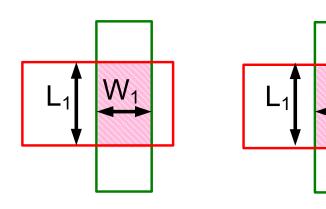

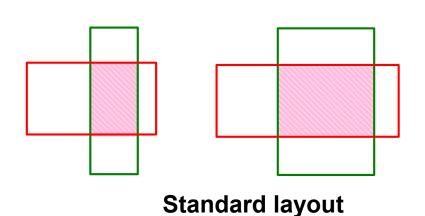

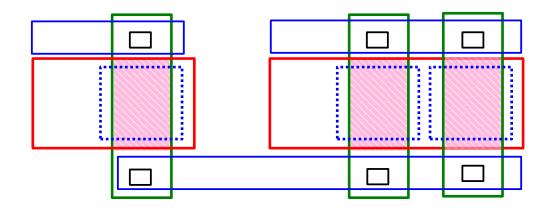

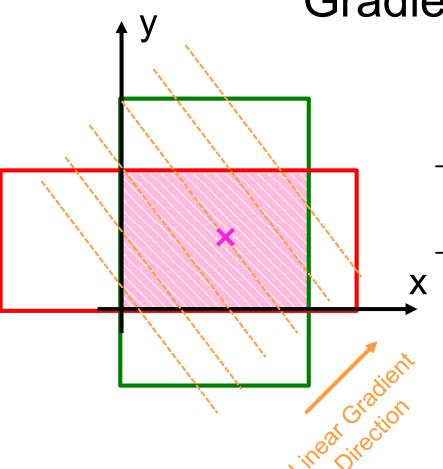

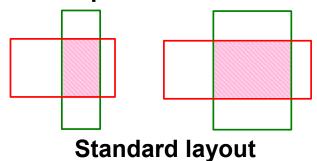

### **Standard layout**

$W_2$

$$\mathsf{M} = \left[ \frac{\mathsf{W}_2 + 2\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_2 + 2\Delta\mathsf{L}} \right]$$

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 2\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] \neq 2$$

Gate area after fabrication depicted

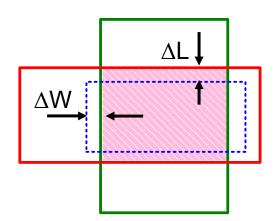

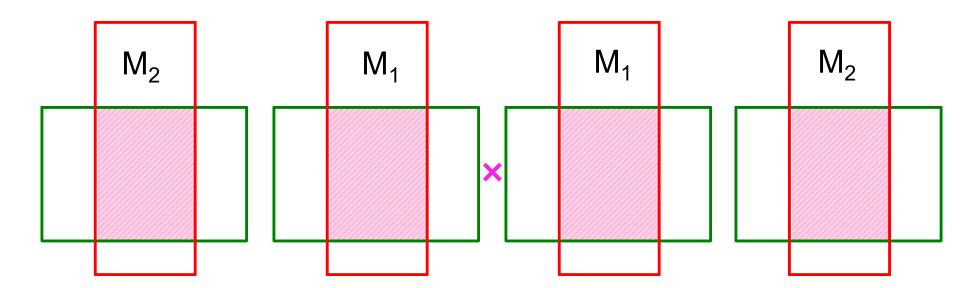

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

$$M = \left[ \frac{2W_1 + 2\Delta W}{W_1 + 2\Delta W} \bullet \frac{L_1 + 2\Delta L}{L_1 + 2\Delta L} \right] \neq 2$$

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] = 2$$

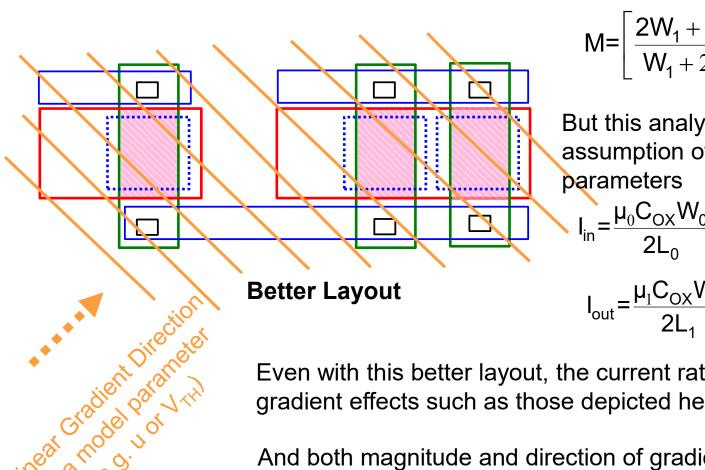

#### **Better Layout**

#### Example with M = 2

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] = 2$$

But this analysis was based upon assumption of matching of process

$$I_{in} = \frac{\mu_0 C_{OX} W_0}{2L_0} (V_{GS0} - V_{T0})^2$$

$$I_{out} = \frac{\mu_1 C_{OX} W_1}{2L_1} (V_{GS1} - V_{T1})^2$$

Even with this better layout, the current ratio will not be 2 if gradient effects such as those depicted here are shown

And both magnitude and direction of gradient effects are a random variable which will vary across a die

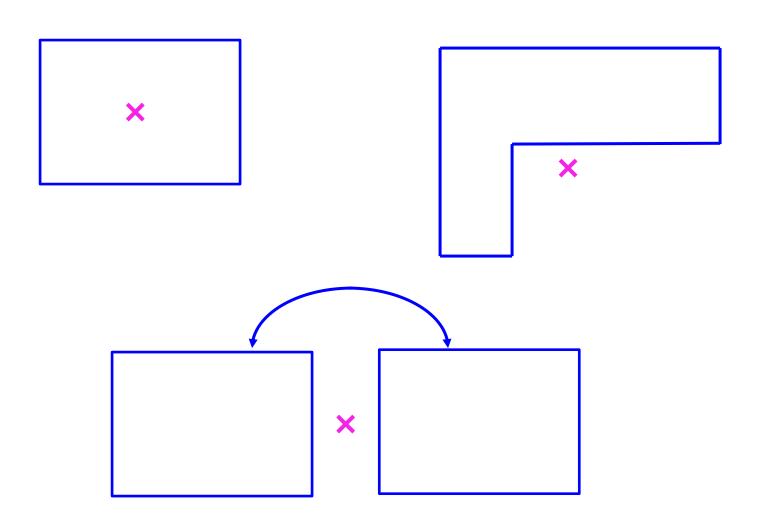

X Denotes Geometric Centroid

Geometric Centroids of Channel

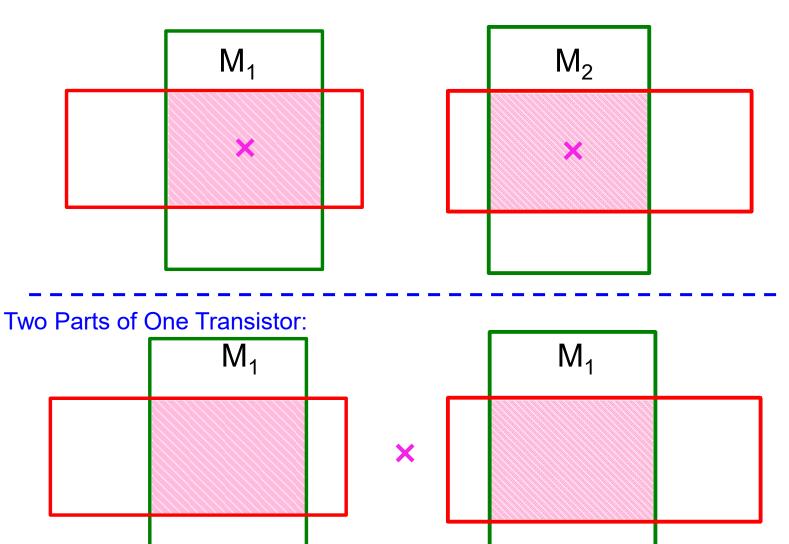

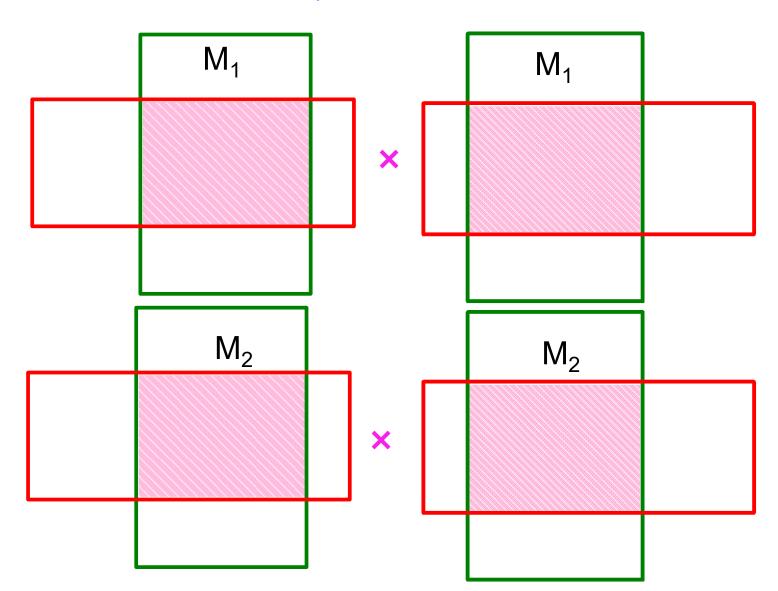

#### Two Transistors:

Two Transistors each with two parts:

Common Centroid for Ideally Matched Devices

Two Transistors each with two parts:

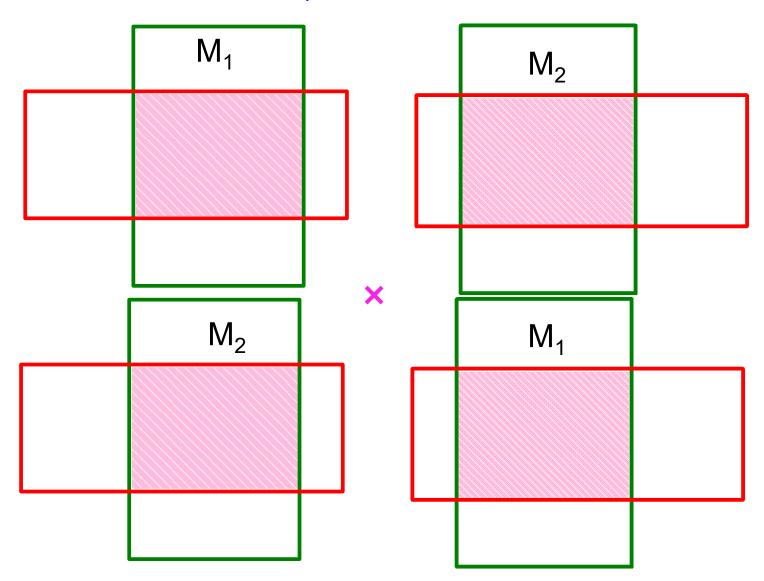

Common Centroid for Matched Devices

Two Transistors each with two parts:

Common Centroid for Ratioed Devices

$$M = \frac{W_2}{W_1} \frac{L_1}{L_2} = 2$$

Two Transistors with different effective widths:

## Gradient

Threshold voltage dependent upon position

$$V_{TH}(x,y)$$

- Significant changes in threshold voltage can occur due to gradient effects

- This can seriously degrade matching in matching-critical circuits

- If the threshold voltage of a transistor changes with position, it can be reasonably accurately modeled with an "equivalent" threshold voltage

- For linear gradient, V<sub>THEQ</sub>=V<sub>TH</sub>(X<sub>C</sub>,Y<sub>C</sub>)

$$\mathbf{X}$$

:  $(\mathbf{X}_{\mathbf{C}}, \mathbf{Y}_{\mathbf{C}})$

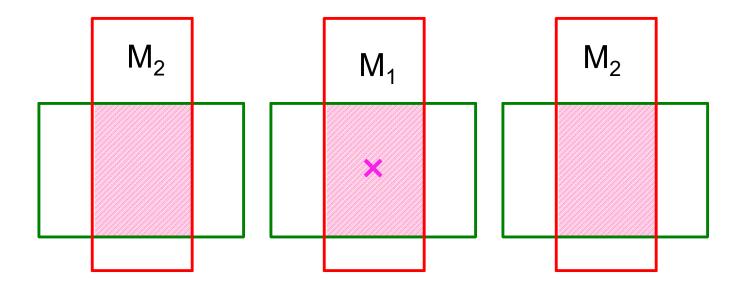

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

$$\mathsf{M} = \left\lceil \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right\rceil = 2$$

$\mathsf{M} = \left| \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right| = 2$

Linear gradient mismatch eliminated with common-centroid layout!

If I<sub>0</sub> is practically generated (it can be), now have available a large number of accurate current sources or sinks that can be used for biasing and for other purposes on chip!

Stay Safe and Stay Healthy!

## End of Lecture 33